# **ECLIPSE** INCUBATION

## CIF documentation (Incubation)

#### Copyright (c) 2010, 2023 Contributors to the Eclipse Foundation

Version v0.10

## **Table of Contents**

| 1. Synthesis-based engineering                                     | 3  |

|--------------------------------------------------------------------|----|

| 1.1. Supervisory controllers                                       | 3  |

| 1.2. Engineering approaches for supervisory controller development | 5  |

| 1.2.1. Traditional engineering                                     | 7  |

| 1.2.2. Model-based engineering                                     |    |

| 1.2.3. Verification-based engineering                              |    |

| 1.2.4. Synthesis-based engineering                                 |    |

| 1.3. Synthesis-based engineering example                           |    |

| 1.3.1. FIFO requirement                                            |    |

| 1.3.2. Synthesis-based engineering                                 |    |

| 1.3.3. Example benefits of synthesis-based engineering             |    |

| 1.4. Synthesis-based engineering in practice.                      |    |

| 1.4.1. Steps                                                       |    |

| 1.4.2. Advanced                                                    |    |

| 1.4.3. Synthesis-based engineering in practice example             |    |

| 1.5. Challenges in applying synthesis-based engineering            |    |

| 1.5.1. Change in way-of-working                                    |    |

| 1.5.2. Tool support                                                |    |

| 2. Language tutorial                                               |    |

| 2.1. Introduction                                                  |    |

| 2.2. Lessons                                                       |    |

| 2.3. Basics                                                        |    |

| 2.3.1. Automata                                                    |    |

| 2.3.2. Synchronizing events                                        | 55 |

| 2.3.3. Non-determinism                                             |    |

| 2.3.4. Alphabet                                                    | 60 |

| 2.3.5. Event declaration placement                                 | 62 |

| 2.3.6. Shorter notations                                           |    |

| 2.4. Data                                                          | 66 |

| 2.4.1. Discrete variables                                          | 66 |

| 2.4.2. Discrete variable value changes                             | 67 |

| 2.4.3. Location/variable duality (1/2).                            | 68 |

| 2.4.4. Location/variable duality (2/2)                             | 69 |

| 2.4.5. Global read, local write                                    | 71 |

| 2.4.6. Monitoring                                                  | 72 |

| 2.4.7. Old and new values in assignments                           |    |

| 2.4.8. The tau event                                               | 80 |

| 2.4.9. Initial values of discrete variables                        | 82 |

| 2.4.10. Initialization predicates                                 |

|-------------------------------------------------------------------|

| 2.4.11. Using locations as variables                              |

| 2.4.12. State (exclusion) invariants                              |

| 2.4.13. State/event exclusion invariants                          |

| 2.5. Types and values                                             |

| 2.5.1. Types, values, and expressions                             |

| 2.5.2. Values overview                                            |

| 2.5.3. Integers                                                   |

| 2.5.4. Ranged integers                                            |

| 2.5.5. Reals                                                      |

| 2.5.6. Booleans                                                   |

| 2.5.7. Strings                                                    |

| 2.5.8. Enumerations                                               |

| 2.5.9. Tuples                                                     |

| 2.5.10. Lists                                                     |

| 2.5.11. Bounded lists and arrays                                  |

| 2.5.12. Sets                                                      |

| 2.5.13. Dictionaries                                              |

| 2.5.14. Combining values                                          |

| 2.5.15. If and switch expressions                                 |

| 2.6. Scalable solutions and reuse (1/2)                           |

| 2.6.1. Constants                                                  |

| 2.6.2. Algebraic variables                                        |

| 2.6.3. Algebraic variables and equations                          |

| 2.6.4. Type declarations                                          |

| 2.7. Time                                                         |

| 2.7.1. Timing                                                     |

| 2.7.2. Continuous variables                                       |

| 2.7.3. Continuous variables and equations                         |

| 2.7.4. Equations                                                  |

| 2.7.5. Variables overview                                         |

| 2.7.6. Urgency                                                    |

| 2.7.7. Deadlock and livelock                                      |

| 2.8. Channel communication                                        |

| 2.8.1. Channels                                                   |

| 2.8.2. Dataless channels                                          |

| 2.8.3. Combining channel communication with event synchronization |

| 2.9. Functions                                                    |

| 2.9.1. Functions                                                  |

| 2.9.2. Internal user-defined functions                            |

| 2.9.3. Function statements                                        |

| 2.9.4     | 4. Functions as values                                     | 143 |

|-----------|------------------------------------------------------------|-----|

| 2.10. Sc  | calable solutions and reuse (2/2)                          | 145 |

| 2.10.     | .1. Automaton definition/instantiation                     | 145 |

| 2.10.     | .2. Parametrized automaton definitions.                    | 146 |

| 2.10.     | .3. Automaton definition parameters                        | 148 |

| 2.10.     | .4. Groups                                                 | 155 |

| 2.10.     | .5. Group definitions                                      | 156 |

| 2.10.     | .6. Imports                                                | 160 |

| 2.10.     | .7. Imports and libraries                                  | 161 |

| 2.10.     | .8. Imports and groups                                     | 162 |

| 2.10.     | .9. Namespaces                                             | 166 |

| 2.10.     | .10. Input variables                                       | 166 |

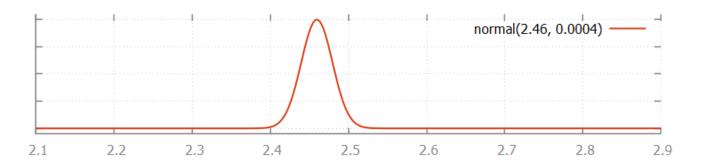

| 2.11. St  | tochastics                                                 | 169 |

| 2.11.     | .1. Stochastics                                            | 169 |

| 2.11.     | .2. Discrete, continuous, and constant distributions       | 170 |

| 2.11.     | .3. Pseudo-randomness                                      | 173 |

| 2.12. La  | anguage extensions                                         | 174 |

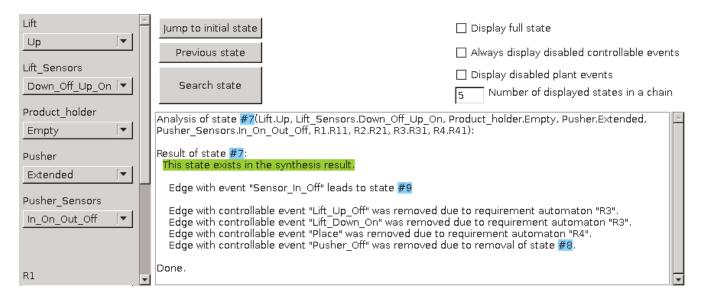

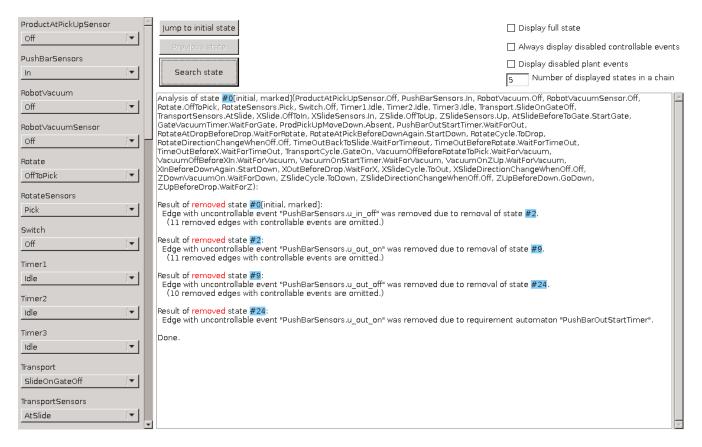

|           | .1. Supervisory controller synthesis                       |     |

| 3. Langua | age reference                                              |     |

| 3.1. Lex  | xical syntax                                               |     |

| 3.1.1     | 1. Keywords                                                |     |

| 3.1.2     | 2. Terminals                                               |     |

| 3.1.3     | 3. Whitespace                                              |     |

| 3.1.4     | 4. Comments                                                | 184 |

| 3.2. Gra  | ammar                                                      | 184 |

| 4. Tools  |                                                            | 197 |

| 4.1. Spe  | ecification tools                                          | 198 |

| 4.1.1     | 1. CIF text editor                                         | 198 |

| 4.2. Sup  | pervisory controller synthesis tools                       |     |

| 4.2.1     | 1. Data-based supervisory controller synthesis.            |     |

| 4.2.2     | 2. Event-based synthesis toolset                           | 248 |

| 4.2.3     | 3. CIF to Supremica transformer                            | 267 |

| 4.3. Sin  | mulation, validation, and verification tools               | 273 |

| 4.3.1     | 1. CIF simulator                                           | 273 |

| 4.3.2     | 2. CIF to mCRL2 transformer                                | 433 |

| 4.3.3     | 3. CIF to UPPAAL transformer                               | 444 |

| 4.3.4     | 4. Controller property checker                             | 447 |

|           | al-time testing, code generation, and implementation tools |     |

| 4.4.1     | 1. CIF code generator                                      | 455 |

|           | 2. CIF PLC code generator                                  |     |

| 4.5. Mis  | iscellaneous tools                                         | 502 |

| 4.5.1. CIF to CIF transformer       |  |

|-------------------------------------|--|

| 4.5.2. CIF merger                   |  |

| 4.5.3. CIF event disabler           |  |

| 4.5.4. CIF explorer                 |  |

| 4.5.5. CIF to yEd transformer       |  |

| 4.6. Scripting                      |  |

| 4.6.1. Introduction to scripting    |  |

| 4.6.2. Overview of scriptable tools |  |

| 5. CIF examples                     |  |

| 6. CIF release notes.               |  |

| 6.1. Version 0.10 (2023-06-30)      |  |

| 6.2. Version 0.9 (2023-03-31)       |  |

| 6.3. Version 0.8 (2022-12-21)       |  |

| 6.4. Version 0.7 (2022-09-30)       |  |

| 6.5. Version 0.6 (2022-07-07)       |  |

| 6.6. Version 0.5 (2022-03-29)       |  |

| 6.7. Version 0.4 (2021-12-17)       |  |

| 6.8. Version 0.3 (2021-10-01)       |  |

| 6.9. Version 0.2 (2021-07-07)       |  |

| 6.10. Version 0.1 (2021-04-02)      |  |

| 7. Developers                       |  |

| 7.1. CIF language modification      |  |

| 8. Legal                            |  |

| Index                               |  |

CIF is a declarative modeling language for the specification of discrete event, timed, and hybrid systems as a collection of synchronizing automata. The CIF tooling supports the entire development process of controllers, including among others specification, supervisory controller synthesis, simulation-based validation and visualization, verification, real-time testing, and code generation. Combined they enable a synthesis-based engineering approach to efficiently and cost-effectively design and implement high-quality controllers.

CIF is one of the tools of the Eclipse  $ESCET^{M}$  project. Visit the project website for downloads, installation instructions, source code, general tool usage information, information on how to contribute, and more.

The Eclipse ESCET project, including the CIF language and toolset, is currently in the Incubation Phase.

The documentation consists of:

- CIF synthesis-based engineering manual

- CIF language tutorial

- CIF language reference manual

- CIF tool manual

- CIF examples

- CIF release notes

- CIF developers manual

- Legal information

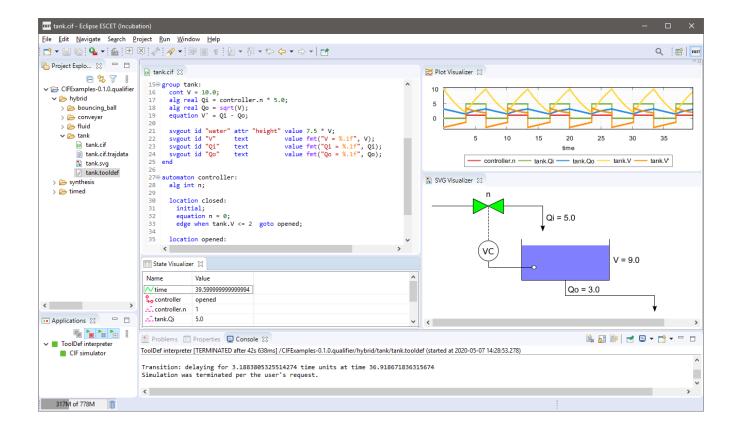

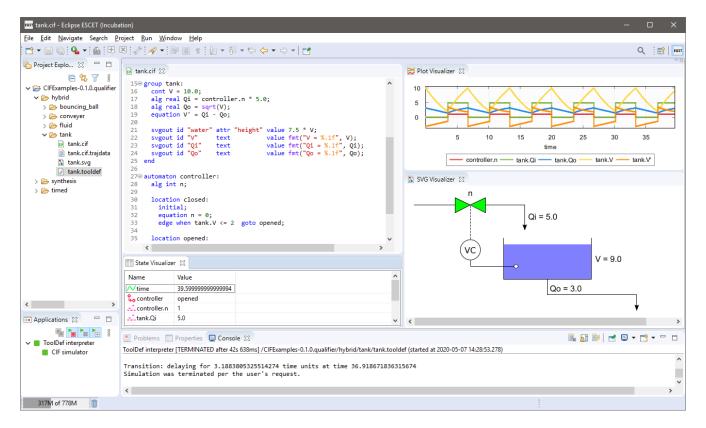

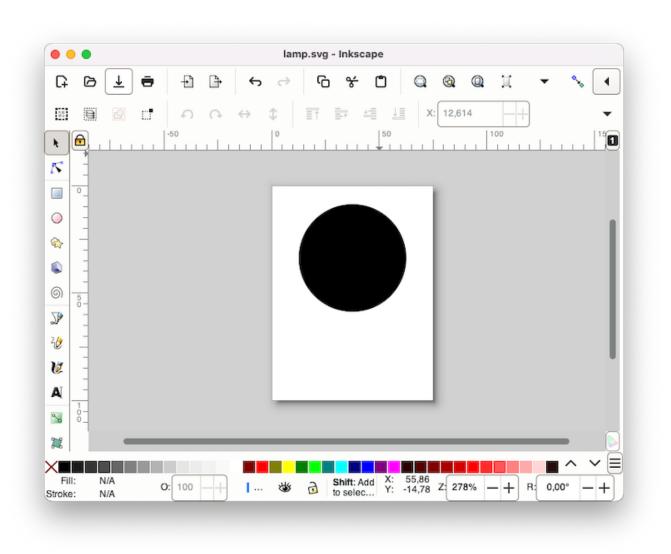

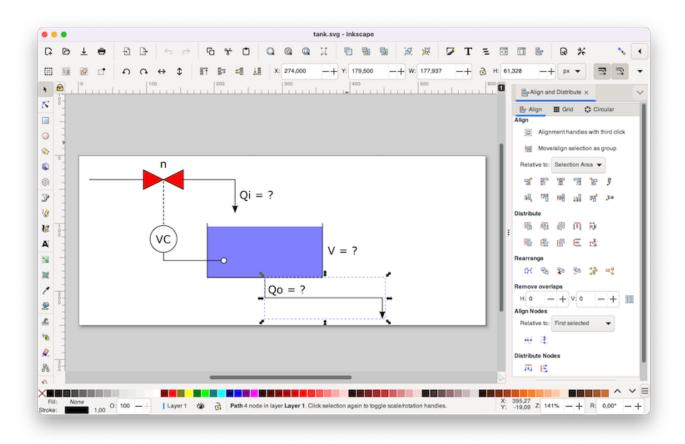

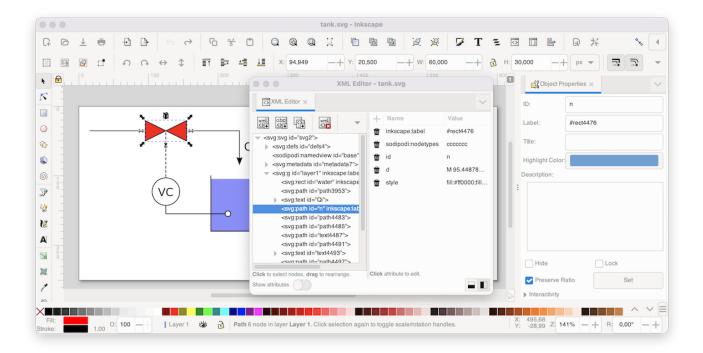

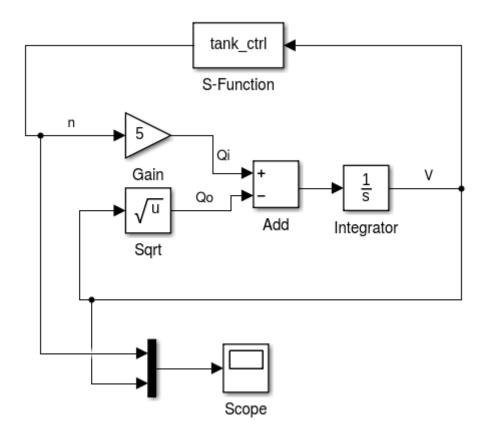

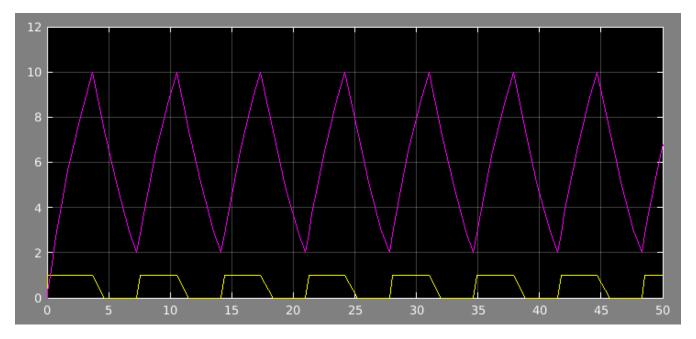

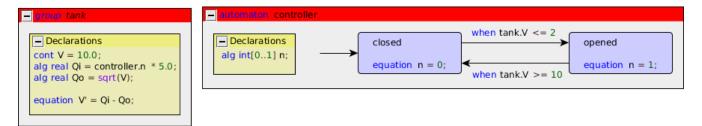

A screenshot showing a CIF model and simulation:

## 1. Synthesis-based engineering

CIF supports synthesis-based engineering, an engineering approach to design and implement supervisory controllers. The engineering approach combines model-based engineering with computer-aided design to produce correct-by-construction controllers. It does so by automating as many steps as possible in the development process.

Supervisory controller synthesis is a main element of synthesis-based engineering, and a key feature of CIF. It involves the automatic generation of supervisory controller models. Implementation of the controller is achieved through (implementation language) code generation, improving speed and reducing the number of errors introduced at this stage. Combined, they allow engineers to focus on *what* the controller should do, rather than *how* it should do it, and how this is to be implemented.

Synthesis-based engineering has many more benefits. As the engineering approach uses welldefined models, designs can be discussed, analyzed, model-checked, or simulated. That allows finding and correcting issues early in the development process, rather than during later stages where correcting them is more costly. It also supports a comprehensive modular design and efficient incremental engineering. Ultimately, this reduces development time and improves the quality of the resulting supervisory controllers.

#### **Supervisory controllers**

Explains what supervisory controllers are, in what types of systems you can find them, and where they are located within such systems.

#### Engineering approaches for supervisory controller development

Discusses synthesis-based engineering of supervisory controllers, its benefits, and its relation to other engineering approaches.

#### Synthesis-based engineering example

Demonstrates the value of synthesis-based engineering through an example.

#### Synthesis-based engineering in practice

Explains concretely how to use the CIF language and toolset to apply synthesis-based engineering of supervisory controllers.

#### Challenges in applying synthesis-based engineering

Explains the challenges of embedding a synthesis-based engineering approach into industrial practice.

## **1.1. Supervisory controllers**

Automated systems are all around us. For instance, hospitals use X-ray and MRI systems, industrial printers print books and magazines, lithography systems are essential for the production of

computer chips, and waterway locks bring ships from one water level to another. In today's digital age, all these systems contain software that controls their operation. Such systems are often called cyber-physical systems, for the *physical* part that consists of the hardware components being controlled, and the *cyber* part that contains the software that controls those physical parts.

Today's cyber-physical systems are often highly complex. To manage their complexity, they are typically step-by-step divided into sub-systems, sub-sub-systems, etc, each with their own responsibility. This way, at the most sub-divided level, *components* are obtained that are small enough to be developed, tested and maintained in isolation. The components are often divided over several layers, to form a layered system architecture.

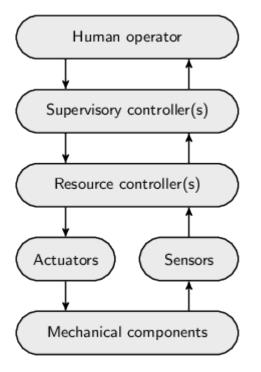

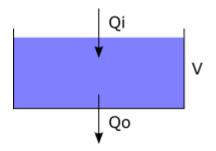

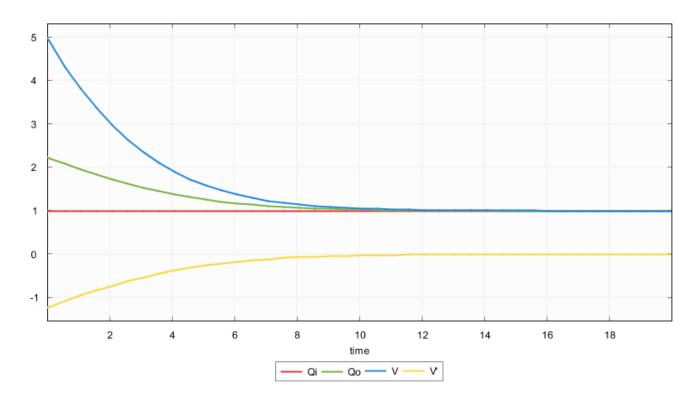

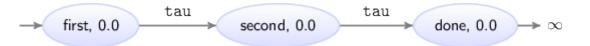

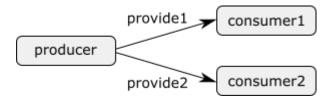

The control of a system can similarly be sub-divided and layered. The following figure shows a traditional view on the control of a system:

At the bottom are the mechanical components, such as motors, switches, levers and valves. Their operation can be steered through actuators and their state of operation can be observed through sensors. Resource controllers provide a first level of control. They may for instance correct for sensor jitter, translate continuous signals to discrete ones, or detect and even correct anomalous situations.

A supervisory controller provides higher-level control. It is typically responsible for the correct and safe behavior of a (sub-)system. For instance, it could be responsible for preventing damage to mechanical components or human operators. It may prevent collisions with or among mechanical components, or prevent mechanical components from overheating. It could control a single sub-system, coordinating one or more resource controllers. However, in case of a layered architecture, it could also coordinate multiple supervisory controllers of a lower layer. Supervisory controllers can thus be found at various levels of a system architecture.

Some systems are fully automated, without the need for human intervention or control. However, most systems provide some kind of human-machine interface that allows a human operator to monitor the system and if necessary control its operation.

Regardless of the exact system architecture, and whether human intervention is possible or not, supervisory controllers play an essential role in the safe control of all kinds of cyber-physical systems, and can be found at various levels within such systems.

## **1.2. Engineering approaches for supervisory controller development**

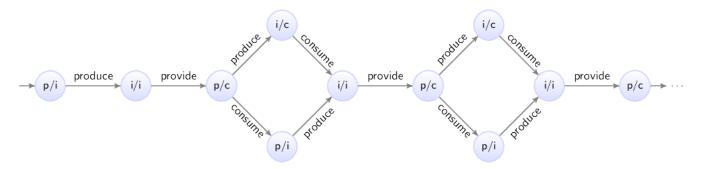

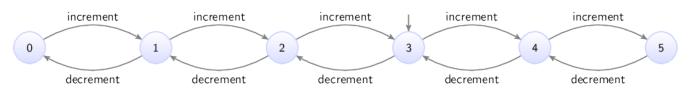

Supervisory controllers can be developed in various ways. The following figure gives an overview. It shows multiple approaches to design and engineer supervisory controllers, as well as how these approaches relate to each other:

| Engineering approach $\rightarrow$               | Traditional<br>Engineering                   | Model-Based<br>Engineering           | Verification-Based<br>Engineering       | Synthesis-Based<br>Engineering       |

|--------------------------------------------------|----------------------------------------------|--------------------------------------|-----------------------------------------|--------------------------------------|

| ↓ Development step                               | Linginooning                                 |                                      | Engineering                             |                                      |

| Requirements design                              | Document-based                               | Document-based                       | Model-based (formal)                    | Model-based (formal)                 |

| Controller design                                | Document-based                               | Model-based (formal)                 | Model-based (formal)                    | Computer-aided (formal)              |

| Realization in software<br>(implementation code) | Traditional software<br>engineering (coding) | Code generation<br>(fault-free code) | Code generation<br>(fault-free code)    | Code generation<br>(fault-free code) |

| Verification<br>(against requirements)           | Testing                                      | Testing +<br>Model-based testing     | Formal verification<br>(model checking) | Correct-by-construction (guaranteed) |

| Validation<br>(of requirements)                  | Testing                                      | Testing +<br>Simulation              | Testing +<br>Simulation                 | Testing +<br>Simulation              |

| Legend: Manual work / Focus                      | (Semi-)automatic                             |                                      |                                         |                                      |

The columns indicate various engineering approaches. From left to right, they employ progressively more automation and computer assistance. The rows of the table indicate typical steps involved in the development of supervisory controllers. The cells indicate for each approach what is involved for the particular step. The green colored cells indicate that the step involves mostly, or at least significant, manual work for the particular engineering approach. Contrarily, the gray colored cells indicate that the step is (mostly) automated for that approach. As the steps with more manual work generally require the most engineering effort, the green cells also indicate where the engineering focus is for a particular approach. Bold texts in cells indicate changes compared to the previous column.

Typical steps involved in the development of supervisory controllers, as represented by the rows from top to bottom, are:

• **Requirements design** focuses on what a controller for a (sub-)system must do. Functional and safety requirements may be specified, for instance requiring that pushing an emergency button stops all motors. Extra-functional requirements may also be specified, for instance requiring that a certain throughput should be achieved.

- **Controller design** focuses on how a controller should satisfy the requirements to efficiently and safely control the system. For instance, the various control states of the system may be specified, as well as how the controller reacts to changing sensor or other input signals by controlling actuators, e.g., enabling a motor.

- Controllers may be **realized in software**. The software source code may for instance be implemented using Java, C or PLC programming languages.

- **Verification** involves checking the realized controller against its requirements design and controller design, to ensure that the controller is correctly realized. The system, controlled by the controller, should behave as designed.

- **Validation** involves checking the realized controller and its design, to ensure that the right controller is made. That is, the requirements must be correct and complete, such that the controller ensures that the system operates safely and efficiently in all circumstances.

Typically, the various engineering approaches as represented by the columns from left to right, can be characterized as follows:

- **Traditional engineering** is document-based. Requirements are written down informally in large requirement documents. They are used as input for controller design documents. The documents are then handed over to a different person, team or supplier, for the implementation. Implementation of the controller in software is done through manual coding. Verification and validation involve testing at various levels, including unit testing, integration testing and system testing. Traditionally, all five steps are performed manually, which is laborious and error-prone.

- Model-based engineering or model-driven engineering automates the realization step, and provides computer assistance especially for the verification and validation steps. It places models at the center of attention. The controller is modeled in a formal way, allowing a computer to interpret and analyze its behavior. That is, it is specified in a mathematically unambiguous way, for instance using state machines. Such models are considered the single source of truth. From them, all kinds of artifacts can be generated automatically, including the software code of the controller's implementation. This ensures that the code is fault-free and behaves consistently with the behavior as expressed by the controller model. The models can also be used to partly automate verification, for instance through the use of model-based testing. Simulation models can be used to simulate the (controlled) system behavior and validate the requirements during early phases of development.

- Verification-based engineering is a form of model-based engineering with computerassistance to automate the verification step. It uses formal verification, or model checking, a mathematical technique that can automatically check the controller model against its requirements. To employ formal verification, both the controller model and the requirements must be formally specified. Formal verification then either indicates that the specified requirements are guaranteed to be satisfied by the controller model, or it provides counter examples that indicate in which situations they are not satisfied. This is exhaustive, as it considers every conceivable scenario, unlike testing, which typically covers only a limited number of scenarios. Through formal verification, the controller model can be iteratively adapted to satisfy all specified requirements in every possible situation.

- **Synthesis-based engineering** is a form of model-based engineering with computer-assistance to automate the design of the controller. It uses supervisory controller synthesis to automatically synthesize a controller model from requirements and a simple model of the to-be-controlled system. This mathematical technique guarantees that the synthesized controller model satisfies all specified requirements. This makes verification of the controller model against its requirements superfluous, as the synthesized controller model is guaranteed correct-by-construction. With the controller design, realization and verification either being automated or unnecessary, only requirements design and validation remain. This allows engineers to focus on *what* the controller should do, rather than *how* it should achieve it.

The use of model-based engineering combined with computer-aided design, through formal methods like formal verification and supervisory controller synthesis, has many advantages. It allows to produce unambiguous, complete, consistent, and up-to-date specifications, leading to higher quality controllers at similar or even lower effort and costs.

After this general comparison of the approaches, the following provides more detailed information:

- Traditional engineering

- Model-based engineering

- Verification-based engineering

- Synthesis-based engineering

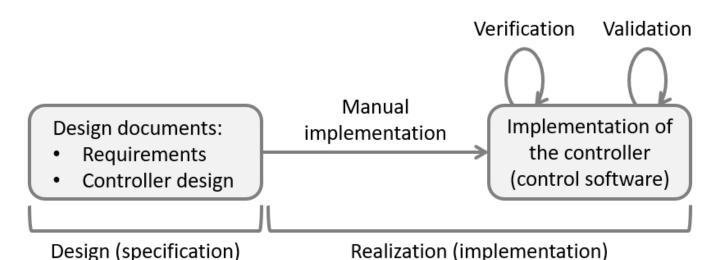

#### 1.2.1. Traditional engineering

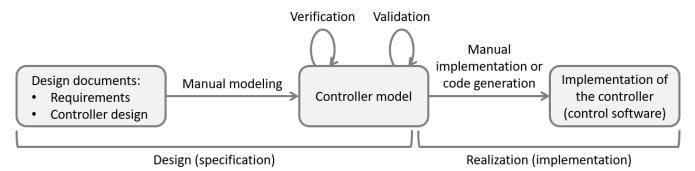

The following figure shows a simplified development process for traditional engineering of supervisory controllers:

Traditionally, controllers are first specified in design documents. They for instance list their functional and safety requirements, describe their control states and indicate when the controller should actuate the various actuators depending on changing sensor signals.

Subsequently, the controller is manually implemented in software code through the use of a programming language, such as PLC code for a PLC platform, or Java or C++ code for an industrial PC.

Finally, the implementation is verified and validated, typically by means of testing. Verification involves checking and ultimately ensuring that the controller satisfies its specified requirements. Validation involves checking that the controller exhibits the desired behavior, and thus ensuring it is the desired controller. Since a controller must satisfy its specified requirements, this includes validating the requirements to ensure they are the desired requirements.

#### Downsides of traditional engineering

Traditional engineering has been around for a long time. Companies typically know what works and what doesn't, and how to work around the various challenging aspects of it. It can work well, particularly for small and simple systems, developed by a well-managed but small team. However, the approach has several disadvantages. These become especially apparent when applying it to develop controllers for larger and more complex systems, developed by multiple teams, or with some development activities outsourced to suppliers:

#### Ambiguity

It is extremely difficult to unambiguously write down the control requirements in a document. Often textual descriptions in natural languages can be interpreted in various ways.

The domain expert who writes the requirements has a certain mental picture in their mind. However, software engineers responsible for realizing these requirements in the software implementation may interpret them differently after forming their own mental picture. There is often a big gap between the specification of the design and its implementation.

The documents may also serve as input or as a contract to a supplier to develop the control

software. Then the impact and costs of ambiguity can be huge, much more so than when the implementation is done in-house within the company.

#### Incompleteness and inconsistency

Besides the interpretation of the requirements also their completeness and consistency is important. Often the normally occurring situations (happy flow) is adequately covered by the requirements. However, the edge cases and exceptional circumstances are just as important, especially when safety is of critical importance to the system.

Consider for instance requirements for when the hardware fails, such as when a cable breaks or a sensor becomes defect. Such cases are often far more complex and the number of combinations/interactions that has to be considered can be immense. Ensuring that the textual descriptions of all these cases do not lead to inconsistencies is often practically undoable.

A good domain expert will be able to limit the number of mistakes, such as missing requirements and contradictions in the requirements specification, but typically can't completely eliminate them. A good software/PLC engineer will surely spot some of the remaining mistakes during the implementation and testing of the controller.

However, even thoroughly tested and delivered industrial code often still contains faults. Furthermore, if the specification is incomplete, software engineers will make their own choices, which may or may not match with what the domain expert had in mind. Again, working with external suppliers, rather than doing the development in-house within the company, may aggravate these concerns.

#### Multi-disciplinary systems

The multi-disciplinary nature of design versus implementation also plays a role. A domain expert may know everything about the functional requirements of the system. The software engineer, especially one from a supplier, may lack such knowledge. They come from different domains, often use different technical terms, and thus essentially speak different languages. This makes it more difficult for them to understand each other, and hinders communication.

#### Abstraction levels

Furthermore, there is a difference in level of abstraction between design and realization. The control requirements are often written as functional specifications. For the implementation numerous details of a lower abstraction level play a role, such as data structures, message encodings and byte orderings. A functional specification typically does not concern itself with such aspects. Again, people from different disciplines and domains may not be able to effectively communicate with each other.

#### Mixing design with implementation aspects

The situation becomes even more complex if (unintentionally) during the design also implementation aspects are incorporated into the functional specification. Then the clear separation between design and realization is lost. This often leads to more misunderstandings, which then requires more communication and collaboration to resolve.

#### **Outdated documentation**

Another aspect to consider for specifications in documentation, is that any changes, such as bug fixes and new features, are often only implemented in the software. After a while the documents become more and more outdated and thus unusable. This increases the gap between specification and implementation.

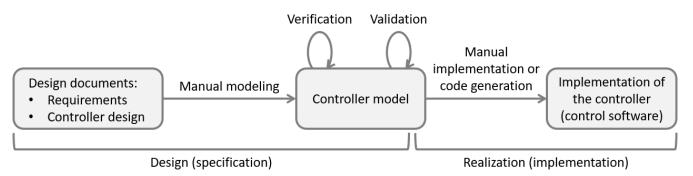

#### 1.2.2. Model-based engineering

Model-based design, model-based software/system engineering and model-driven engineering, are related terms. They place models at the center of the entire development process and the entire lifecycle of the system, including design, implementation and maintenance. The models fill the gap between the specification and implementation.

#### Model-based engineering process

The following figure shows a simplified development process for model-based engineering of supervisory controllers:

At the center is a controller model, a model of a controller that unambiguously specifies how the controller works. It precisely specifies how the state of the controller changes when a sensor signal changes, and under what conditions and in which states an actuator may be turned on or off. Ideally, the model has a mathematical foundation. It may for instance be modeled as one or more state machines.

The controller model is manually modeled from design documents. They for instance list the functional and safety requirements of the controller, describe its control states and indicate when it should actuate the various actuators depending on changing sensor signals.

The controller model must be verified and validated. Verification involves checking and ultimately ensuring that the system, controlled by the controller, satisfies its specified requirements. Validation involves checking that the controller ensures the desired system behavior, and thus ensuring it is the desired controller. Since a controller must satisfy its specified requirements, this includes validating the requirements to ensure they are the desired requirements. This may be supported by formal methods, methods with a mathematical foundation, and supported by computer tools. For instance, a controller model may be simulated. This may reveal issues, that can be addressed to improve the controller model.

The control software is typically implemented using a programming language, such as PLC code for a PLC platform, or Java or C++ code for an industrial PC. This may for instance be done in-house within the company, by different teams or departments, or by a supplier. While manual implementation is possible, the code is often automatically generated from the controller model.

#### Benefits of model-based engineering

Model-based engineering directly addresses many of the downsides of traditional engineering:

#### Unambiguous and intuitive specifications

It is important that the models are formal models, with a mathematical meaning (semantics). Examples of formal models are state machines to model controllers and logical formulas for model requirements. The use of such formal models leads to unambiguous interpretation of control requirements and controller behavior.

The use of the right formal language, in which control requirements can be specified in an intuitive manner is essential. This is where domain specific languages (DLSs) play a role. Such a language closely matches the world of the domain experts, such that they can directly write their control requirements in a notation that fits how they think about the system. This leads to readable and unambiguous specifications.

Besides specific to a domain, domain specific languages are also more restrictive in what you can write down than a general programming language. While this seems to be a limitation, it is actually their strength. Due to the limited number of concepts to consider, there are less different ways to model a system. This further reduces ambiguity, due to more consistency and simpler specifications.

#### Bridges the multi-disciplinary specification/implementation gap

Using a good domain specific language, both domain experts and software engineers can understand and interpret the specification in the same way, regardless of their different backgrounds. Obviously, the language must be rich enough to properly describe all relevant aspects of the domain. It must also use a proper abstraction level.

#### Complete and consistent specifications through computer-aided validation and verification

The use of unambiguous formal models has even more advantages, as it makes it possible for a computer to interpret and analyze the models. The limited concepts of the domain specific

language help to do so efficiently and scalably. Computers can with formal methods, mathematical techniques, quickly and accurately analyze countless scenarios. This is a great advantage compared to traditional document reviews.

An example of this is verification by means of model-based testing. Instead of manually writing dozens or hundreds of tests, a computer can automatically generate thousands, millions or even more tests from the controller model. This allows covering much more behavioral scenarios, increasing confidence in correctness of the controller model and its implementation.

Another example of this is validation of the specification by means of simulation. Using simulation various execution scenarios can be examined, to give insight into the behavior of the system being controlled by the controller. This provides new insights that can be used to further improve the specification. Especially for complex situations, which are difficult to understand, this is of great value.

The use of computer-aided verification and validation often exposes issues in the specification. Model-based testing for instance, may find that a certain scenario was not considered during controller design, and therefore does not satisfy the requirements. The controller model may then be adapted and tested again. This allows to effectively and iteratively improve the design, leading to more complete and consistent specifications, and therefore to better quality controllers.

#### Address issues early to reduce effort and costs

A great benefit of model-based engineering is that verification and validation can be done already during the earlier phases of development, rather than only at later phases such as implementation or testing. It is well-known in industry that the later a mistake is found and fixed, the higher the effort and costs to do so. In practice, implementations developed using model-based engineering approaches are often produced more efficiently and with less mistakes. Through automation, changes can be incorporated more quickly into the models, and these can automatically be analyzed again.

Furthermore, the benefit of discussions that may arise early on during the development process, for instance about how the specification must be adapted if it is found lacking, is not to be underestimated. It is of great value that so early on it is possible to discuss control requirements and the behavior of the system during unforeseen circumstances, such as when a sensor is defect.

#### Efficiently obtain correct-by-construction implementations

After several iterations the confidence in the controller specification is sufficiently high, and thus the chance of incompleteness and inconsistencies sufficiently low, given the amount of effort and money that can reasonably be spent during the development process. The development process produces an implementation-independent model of the control logic, that during the realization can be implemented. This may be done by a different team or department

within the same company, or even by an external supplier. The formal specifications can then serve as a contract with the third party, allowing for more control. They can also be used to perform acceptance tests on the implementation.

While the controller can be manually implemented based on the controller model, automatic generation of the control software is often a better choice. Automation prevents the kinds of subtle mistakes that humans make when they manually implement something, ensuring consistency between the specification and the implementation. Automation also improves efficiency. If the controller model is changed, with the push of a button a new correct-by-construction implementation can quickly be generated from it.

#### Implementation-independent models separate design from implementation

Since a controller model is implementation-independent, there is a clear separation between design (specification) and realization (implementation). It allows generating implementation code for different platforms, such as industrial PCs or PLCs, with different programming languages, such as Java, C or PLC code, for 32 or 64 bits architectures, etc. Additionally, controller models are vendor-independent, allowing to for instance generate PLC code for PLCs from different vendors. It is also possible to switch to a different platform or vendor at a later time, or additionally generate code for other platforms or vendors.

#### Up-to-date models are the single source of truth

Model-based engineering places models at the center of attention. It is the models that are adapted if they are functionally incorrect, have inconsistencies, or new functionality is required. Techniques such as model-based testing, simulation, and code generation all operate on the models. The models are therefore the 'single source of truth'. Contrary to documents, the models will be maintained. They remain up-to-date as they are the basis of all development during the entire life cycle of the system, including design, realization and maintenance.

The use of model-based engineering combined with computer-aided design through formal methods thus has many advantages. It allows for producing unambiguous, complete, consistent, and up-to-date specifications, leading to higher quality controllers at similar or even lower effort and costs. However, specific forms of model-based engineering, such as verification-based and synthesis-based engineering, can offer additional benefits.

Even though model-based engineering has many benefits, companies should not underestimate how significantly different it is from traditional engineering. They should consider and manage the challenges particular to this engineering approach.

#### Terminology

The following terminology is often used when discussing model-based engineering of supervisory controllers:

#### **Code generation**

The automatic generation of correct-by-construction control software from a controller model.

#### **Control requirements**

Properties that a system must satisfy, even if they are not satisfied in the uncontrolled system. Examples include functional and safety properties. They are called control requirements, or simply requirements.

#### **Control software**

The implementation of the controller in software. For instance, PLC code for a PLC platform, or Java or C++ code for an industrial PC.

#### **Controller model**

A model of a controller that unambiguously specifies how the entire controller works. Also called a supervisory controller, or simply controller, in control theory. It precisely specifies how the state of the controller changes when a sensor signal changes, and under what conditions and in which states an actuator may be turned on or off.

#### **Controller validation**

The process of checking and ultimately ensuring that the system being controlled by a controller exhibits the desired behavior, and thus ensuring that the controller is the desired controller. Since a controller (model) must satisfy its specified requirements, this includes validating the requirements to ensure they are the desired requirements.

#### **Controller verification**

The process of checking and ultimately ensuring that the controller satisfies its specified requirements.

#### Domain-specific language

A modeling language with concepts specific to a certain domain. This can for be the domain of supervisory controllers with concepts such as plants and requirements, or the domain of office lighting systems with concepts such as lamps and occupancy sensors.

#### **Formal method**

A method with a mathematical foundation, typically supported by computer tools. For instance,

formal verification or supervisor synthesis.

#### Model

An unambiguous representation of all relevant concepts, ideally with a mathematical foundation. For instance, a model of control requirements in the form of logical formulas, or a model of a controller represented as a state machine.

#### Model-based development/engineering

Places models at the center of the entire development process and the entire lifecycle of the system, including design, implementation and maintenance.

#### **Modeling language**

A language in which models can be specified, in an unambiguous way, and ideally also with mathematical foundation.

#### 1.2.3. Verification-based engineering

Verification-based engineering is a form of model-based engineering. It uses formal verification to automate the verification that the controller model satisfies its requirements.

#### Verification-based engineering process

The following figure shows a simplified development process for verification-based engineering of supervisory controllers:

The verification-based engineering process is very much similar to the model-based engineering process. The only difference is the way the verification of the controller (model) against its specified requirements is performed. Verification-based engineering uses formal verification, or model checking, to mathematically prove a certain property holds. Such properties could for instance be the absence of deadlock or livelock, or that a bridge may only open if its corresponding traffic lights

have been set to signal a red light. Formal verification can prove that such properties hold for every conceivable scenario.

If a property does not hold, formal verification produces counter examples, typically in the form of a sequences of inputs that lead to states in the controller model where the property is not satisfied. This makes it possible to pinpoint the problem in the model, and address it. It is often an iterative process to address such issues, perform verification again, address more issues, perform verification again, etc. If no counter examples are produced, all verified properties are guaranteed to be satisfied by the controller model.

To employ formal verification not only the controller model must be formally specified, but also the properties to check. This means that the requirements are no longer specified in natural language in documents, but in mathematically unambiguous specifications. An example is state machines that define the order in which things may happen, such as that a certain sensor must go on before an actuator can be enabled. Another example is logical formulas that indicate that certain combinations of states in the controller models should never occur, e.g., they could indicate a collision that is to be prevented.

#### Benefits of verification-based engineering

Verification-based engineering has all the benefits of model-based engineering. Additionally, it has the following benefit:

#### Formal verification guarantees that the requirements are satisfied

Formal verification considers every conceivable scenario. It can therefore mathematically prove that a specified requirement is satisfied by the controller (model). It is thus more powerful than testing, which typically covers only a limited number of scenarios and is then not exhaustive.

Even though verification-based engineering has many benefits, companies should not underestimate how significantly different it is from traditional engineering or even from lesserautomated forms of model-based engineering. They should consider and manage the challenges particular to this engineering approach.

#### 1.2.4. Synthesis-based engineering

Synthesis-based engineering is a form of model-based engineering. It uses supervisory controller synthesis (or simply supervisor synthesis) to automatically synthesize a correct-by-construction controller model.

#### Synthesis-based engineering process

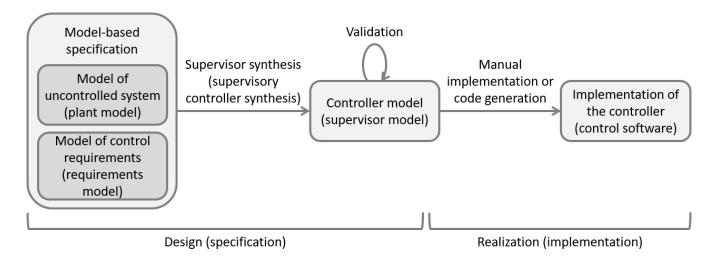

The following figure shows a simplified development process for synthesis-based engineering of supervisory controllers:

As with general model-based engineering, at the center is a controller model with a mathematical foundation. From the controller model, the control software can still be manually implemented or automatically generated.

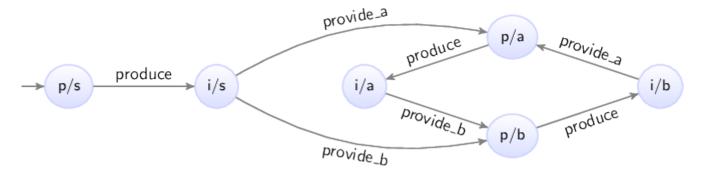

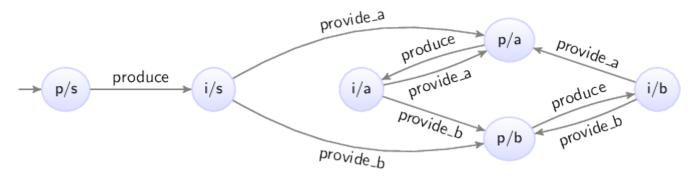

However, with synthesis-based engineering, the controller model is not manually modeled from design documents. Instead, it is automatically generated from models of the uncontrolled system (plant model) and control requirements (requirements model).

Verification to ensure that the controller (model) satisfies its specified requirements is then superfluous, as the synthesized controller model is correct-by-construction. The controller model must however still be validated to ensure it behaves as intended. The specified requirements could not be the desired requirements, as they could for instance be wrongly specified or too strict, resulting in the system being controlled by the controller exhibiting unwanted or insufficient behavior.

#### Input: plant and requirements models

Supervisor synthesis requires two types of models as input. The first type of model is called a *plant* model, after the concept of <u>plant</u> from <u>control</u> theory. Plant models describe capabilities or behavior of a physical system 'as is', without any integrated control. They represent the possible behavior of the uncontrolled system. The second type of model is called a *requirements* model. Requirements models describe the requirements that the controller must adhere to. They model restrictions upon the behavior of the plants, to ensure that only the desired behavior remains.

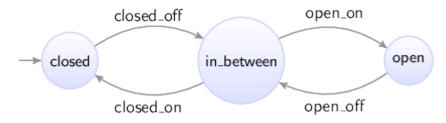

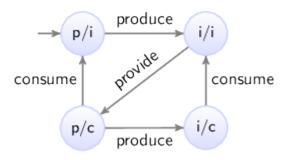

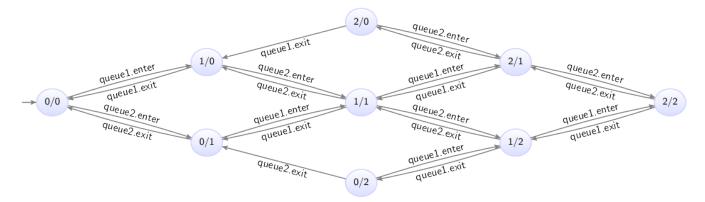

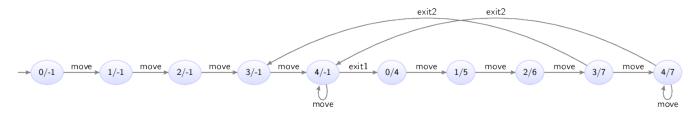

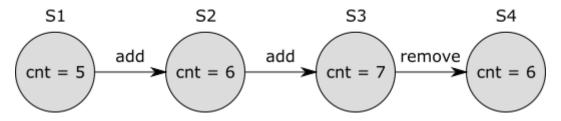

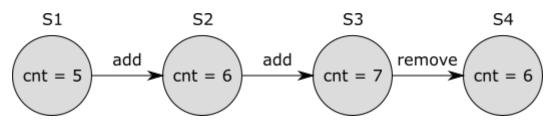

A plant model can for instance specify which sensors and actuators are present in the system. It may also specify their interdependencies. For instance, a sensor that indicates that a gate is open and a sensor that indicates it is closed, can under normal circumstances not be enabled at the same time. A plant model is often modeled as a state machine. The following figure shows as an example a the combined plant model for the two gate sensors:

Initially it is closed. As the gate is opened, the gate closed sensor goes off, and the gate is somewhere in between. Then it can be closed again, making the gate closed sensor go on. But the gate can also keep going further open, until it is fully opened, and the gate open sensor goes on. There is can be closed again, making the gate open sensor go off. The plant model clearly states that it is not possible for the gate to be open and closed at the same time, as the plant model can only be in one state at a time.

Actions, such a sensor going on or off, or an actuator being turned on or off, are called *events*. Supervisor synthesis distinguishes two types of events, *controllable* and *uncontrollable* events. Controllable events can be controlled by the supervisory controller. Actuators are typically modelled as controllable events, such that the supervisory controller decides when to actuate them. Uncontrollable events operate autonomously, from the perspective of the supervisory controller. A controller can not prevent such events from occurring in the system. For instance, a user may push a button and the corresponding sensor will indicate whether the button is pushed or not. The events to indicate changes in the status of the sensor will happen. The supervisor can not prevent this. Another example of uncontrollable events is limit sensors of movements. When a movement is completed, its limit sensor will be activated, leading to an uncontrollable event being fired.

Plant models at the relatively low abstraction level of sensors and actuators are quite common. However, modeling and controlling (sub-)systems at a higher abstraction level is possible as well. See for more information the section on supervisory controllers.

A requirements model captures requirements. It may specify functional requirements, safety requirements, etc. For instance, the motor to open a gate may only be activated once the barrier to stop traffic is fully closed. Control requirements can also be specified as state machines, but often the use of a logical formula is more intuitive. Combining them is also possible. Well-formulated logical formulas are easy to understand, even for people without a mathematical background. As an example, consider a requirement in three forms: natural language, mathematical formula, and modeled in CIF:

- Natural language: "The actuator to open the gate may only be activated if the barrier is fully closed."

- Mathematical formula: gate\_open\_actuator.c\_on  $\Rightarrow$  barrier\_sensors.closed

- Modeled in CIF as a state/event exclusion requirement:

requirement gate\_open\_actuator.c\_on needs barrier\_sensors.closed;

#### Supervisory controller synthesis

Supervisory controller synthesis generates from the plant and requirements models a controller model, a model of the control logic, named a *supervisor* or supervisory controller. The synthesized supervisor is correct-by-construction, i.e., it satisfy all the requirements in every situation.

The supervisor may be represented as another state machine, but it may for instance also be a list of conditions under which actuators may be activated or deactivated. The synthesized supervisor as a state machine, or the plant model together with the supervisor in the form of extra synthesized control conditions, forms the *controlled system*.

The controlled system is guaranteed to satisfy the following properties:

- **Safe:** It satisfies all specified requirements in all situations that the specified uncontrolled system can be in.

- **Controllable:** It only limits controllable events of the plant, e.g., it may prevent enabling or disabling an actuator, but can't prevent a sensor from going on or off.

- **Non-blocking:** It doesn't block, i.e., a marked state can always be reached from every reachable state, thus ensuring a form of liveness.

- **Maximally permissive:** It does not impose more restrictions than strictly necessary to enforce the previous properties, i.e., it is maximally permissive. In other words, the controlled system permits all safe, controllable, and non-blocking behaviors, i.e., it is minimally restrictive.

In practice the terms *supervisor* and *controller* are often used interchangeably. Formally however, they can be different. A *supervisor* is maximally permissive and may still allow multiple (safe) choices, for instance between enabling multiple different actuators, or between enabling one actuator and disabling another one. A *controller* is considered to explicitly choose specific controllable events rather than allowing multiple ones.

#### Benefits of synthesis-based engineering

Synthesis-based engineering has all the benefits of model-based engineering. Additionally, it has the following benefits:

#### Computer-aided design for improved quality at reduced effort and cost

Computer-aided design and automation shorten the development cycle and reduce human errors. This improves the quality and reliability of controllers, and reduces effort and costs.

More concretely, supervisor synthesis provides computer-aided design assistance. It can for instance automatically detect conflicting requirements. It will also detect that a certain activator may never be enabled in a certain state, because under certain specific conditions this may *later* lead to an unavoidable unsafe state. For complex systems, this kind of situations are often difficult to foresee for human beings. It is therefore difficult to correctly manually model them in a controller model.

#### Focus on the *what* rather than the *how*

With synthesis-based engineering the controller model is automatically synthesized. From it, the implementation is automatically produced through code generation. Verification is not needed as the implementation is correct-by-construction. This essentially only leaves requirements design and validation to focus on. Engineers can thus focus on '*what* should the controller do' (its requirements), rather than on '*how* must the controller achieve this' (the controller design and implementation).

An example is specifying a First-In-First-Out (FIFO) requirement. While specifying it may be quite easy, realizing the requirement in a controller model may be complex due to the various situations that may arise in the system. Supervisory controller synthesis can evaluate all possible combinations of conditions and synthesize a controller that is mathematically correct for all of them. This kind of design automation is even more useful when multiple, complex and related requirements need to be considered. The synthesized supervisor is correct-by-construction for all requirements in all situations, preventing human errors.

#### Verification exposes problems, synthesis solves them

Synthesis-based engineering goes far beyond verification-based engineering. Formal verification exposes problems. It tells you that the controller model is not correct and in which situations, and you need to iteratively adapt it yourself. Each time formal verification produces a counter example to indicate a requirement violation, the controller model needs to be manually adapted. Contrary, supervisor synthesis provides solutions. It automatically synthesizes a controller model that satisfies all the requirements. Synthesis produces in one go a supervisor with all the additional conditions that must be enforced to ensure all requirements are satisfied. This makes verification of the controller model against its requirements superfluous, as the synthesized controller model is already correct-by-construction.

#### Maintain maximum design space freedom

Maximal permissiveness ensures that maximum design space freedom is maintained. When manually designing a controller, an engineer may favor simple control conditions that severely limit the design space. As synthesis produces maximally-permissive supervisors, it imposes minimal restrictions, while still satisfying all requirements. This leaves design space freedom to e.g. choose performance-optimal solution among safe alternatives. A performance-optimal *controller* may for instance be derived from a *supervisor* model that allows multiple (safe) choices.

#### Supports a comprehensive modular design and efficient incremental engineering

Each part of the plant and each requirement can be specified separately. This way it is easy to adapt specific plants or requirements, or add new ones. Modular specifications thus allow for efficient incremental engineering, as after each change a simple re-synthesis is enough to obtain a new correct-by-construction controller.

#### Supports reuse and standardization

The separately specified plants and requirements can even be put in libraries with reusable standardized building blocks. This allows engineers to easily build up new specifications from existing proven building blocks, combining them in different ways. Ultimately this leads to more uniformity and improves efficiency.

#### Intuitive specifications with fine-grained requirement traceability

Each plant and requirement can be specified separately, and has a clear purpose. This provides a good overview of the control requirements, and allows for fine-grained requirement traceability. This unlike the controller model itself. There, one requirement can have an effect on various parts (states) of the controller. It can thus be spread out over the controller model, and mixed with other requirements. Clear modular specifications avoid hiding undesired and unneeded behavior in a large/complex controller.

See the synthesis-based engineering example section for a concrete example that shows the power of synthesis.

Even though synthesis-based engineering has many benefits, companies should not underestimate how significantly different it is from traditional engineering or even from lesser-automated forms of model-based engineering, such as verification-based engineering. They should consider and manage the challenges particular to this engineering approach.

#### Terminology

The following terminology is often used when discussing synthesis-based engineering of supervisory controllers, in additional to model-based engineering terminology:

#### Controllable event

An event that is controlled (enabled or disabled) by the controller. Events to actuate (turn on or off) an actuator are often controllable events.

#### **Controlled system**

The uncontrolled system together with a supervisor or controller that controls it. This may be represented as a single state machine, or as a combination of the \_plant model with the supervisor or controller model.

#### Controller

A controller model that explicitly chooses specific controllable events, rather than allowing multiple ones as a *supervisor* may do. When this distinction is not relevant, *supervisor* and *controller* are often used interchangeably.

#### Correct-by-construction formal method

A formal method that guarantees that the result of the method satisfies all requirements.

#### Event

An action representing something that can happen in the system. For instance, there may be low-level actions for sensors going on or off, and actuators being turned on or off. There may also be higher level actions, such as a command to move an object from one location to another, a command to turn an entire subsystem on or off, or an event through which a subsystem indicates that an error has occurred.

#### Synthesis-based engineering

A form of model-based engineering that uses supervisory controller synthesis (or simply supervisor synthesis) to automatically synthesize a correct-by-construction controller model.

#### **Supervisor**

A maximally permissive controller model that may still allow multiple (safe) choices. Unlike a *controller*, it may for instance allow a choice between enabling multiple different actuators, or between enabling one actuator and disabling another one. When this distinction is not relevant, *supervisor* and *controller* are often used interchangeably.

#### Supervisor synthesis

A correct-by-construction formal method that automatically synthesizes a *supervisor*. It involves the automatic generation, or synthesis, of a correct-by-construction controller model from a simple model of the to-be-controlled system and a model of the control requirements. This is also called controller synthesis or supervisory controller synthesis. Supervisor synthesis makes verification of the resulting controller model against its requirements superfluous. Validation of the resulting system being controlled by the controller (model) is still needed to ensure the

specified requirements are indeed the desired requirements.

#### Uncontrollable event

An event that operates autonomously, from the perspective of the controller. Such events are not controlled by the controller, which can thus not prevent them from occurring. For instance, events of a sensor could indicate that a button was pushed or released. And events of a movement limit sensor could indicate that a movement has reached the end position, or that the moving object is no longer at that position.

#### Uncontrolled system / plant

The uncontrolled system is the system 'as is', without any control. It is also called a plant in control theory. For instance, at a low abstraction level, this could be the individual actuators and sensors of a system. At a higher abstraction level, it could be a collection of controllers for subsystems.

## 1.3. Synthesis-based engineering example

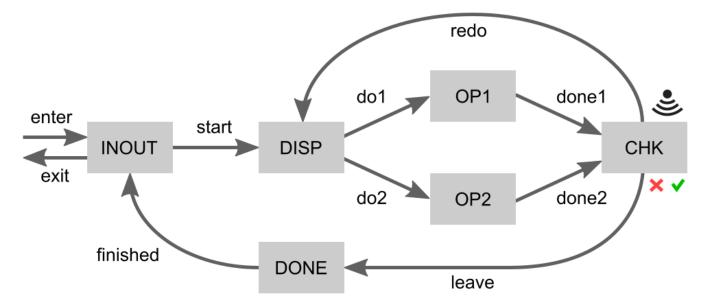

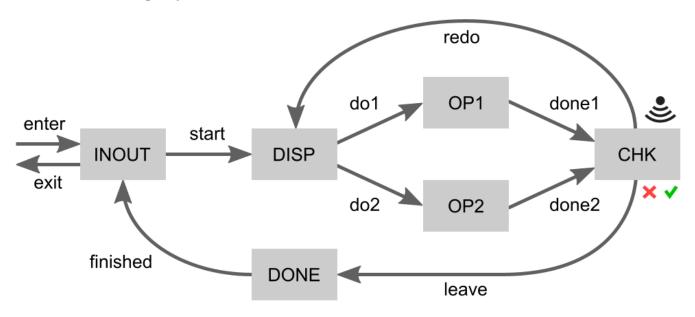

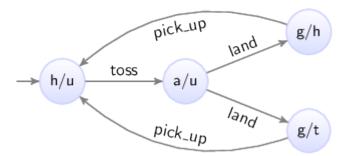

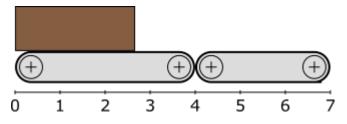

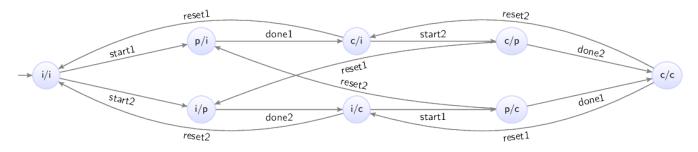

To demonstrate the value of synthesis-based engineering, let's look at an example. The following figure illustrates an example manufacturing system that processes products:

Products *enter* at the *INOUT* place. From there production can *start* by moving them to the dispatcher (*DISP*). The dispatcher dispatches a product (*do1* or *do2*) to one of two operators (*OP1* or *OP2*) that perform the same operation. Once the operation is completed (*done1* or *done2*), the product is moved to the checker (*CHK*). The checker determines whether the operation has completed successfully or has failed. If it has failed, the system must *redo* the operation on that product. This may be repeated until the operation is successful. The product must then *leave* the processing loop, moving to *DONE*. It is then *finished* and moves back to *INOUT*. There it may *exit* the system.

The gray boxes indicate places where at most one product can be located at a time. The moving of products through the system is visualized by the labeled arrows in the figure. Each arrow corresponds to an actuator under the control of the controller. The controller can thus decide when to move products from one place to another. A sensor indicates the result of the check performed on processed products, indicating whether they are OK or not. This sensor works autonomously and is thus not controlled by the controller.

#### 1.3.1. FIFO requirement

The example system, without any controller that controls it, already ensures that:

- Products that *enter* can only *start*, preventing them from exiting without having been processed.

- Products that failed processing must *redo* the operation.

- Successfully processed products must *leave* the operation area.

- Once a product passed *finished* it must *exit*, preventing it from being processed again.

For this example, we consider only a single requirement:

• Products must enter and exit the system in FIFO order.

That is, if one product enters earlier than another, it must also exit earlier.

Without additional control, the system does not satisfy this requirement, as it is possible for multiple products to enter the system and subsequently be processed concurrently. Then, if a later product finishes the operation earlier, or the earlier product requires rework, the later product may be done sooner and thus exit the system earlier. The controller must restrict the behavior of the system such that it satisfies the requirement. It can only do so by controlling the movement of products through the system.

The FIFO requirement is specified in natural language as a short and simple sentence. It can similarly be quite easily modeled, by tracking the order that products *enter* and *exit* the system. Each product that enters the system is given a unique identifying number, one higher than the previous product. As products *exit* the system, the identifier of the last product that exited the system is stored (*lastExitId*). When a product is about to exit the system, it is in the *INOUT* place. If the identifier of the current product on the *INOUT* place is given by *curId*, then the requirement can be formulated as:

• *curId* = *lastExitId* + 1

See the section on synthesis-based engineering in practice example section for how the example system and its requirement can be modeled in CIF.

#### 1.3.2. Synthesis-based engineering

There are various ways to ensure the FIFO requirement holds. A silly solution is to never allow products to enter the system. As there are then no products in the system, products also never leave the system. Therefore, all (non-existent) products are in FIFO order. Another slightly more useful option is to only allow a single product to be processed at a time. This would however severely limit

the productivity of the system. It is actually not that trivial to decide the exact conditions under which the products may move, while still ensuring the FIFO requirement is satisfied.

We can however automatically compute the conditions that must hold for each movement by applying supervisory controller synthesis. This computes for each movement the minimal restriction that must be applied to enforce the requirement. Through synthesis, we obtain a supervisory controller that restricts four movements:

- 1. Movement *start* is only allowed if one of the following two conditions holds:

- At the *DISP* place, *OP1* place, *OP2* place, and *CHK* place, there is in total at most one product.

- At the *DISP* place, *OP1* place, and *OP2* place, there is in total at most one product. There is also a product at the *CHK* place and the check indicates the product was successfully processed.

- 2. Movement *done1* is only allowed if the following two conditions both hold:

- Either there is no product at the *DISP* place, or it is a later product than at the *OP1* place.

- Either there is no product at the *OP2* place, or it is a later product than at the *OP1* place.

- 3. Similarly, movement *done2* is only allowed if the following two conditions both hold:

- Either there is no product at the *DISP* place, or it is a later product than at the *OP2* place.

- Either there is no product at the *OP1* place, or it is a later product than at the *OP2* place.

- 4. Movement *enter* is only allowed if less than four products are in the system.

But why are these the 'optimal' restrictions?

It is important to realize that:

- A. If a product is checked and found to be successfully processed, it can only *leave*. It can not be reprocessed (*redo*). If a product is moved to *CHK* too early, a product that should exit the system before it can't overtake it anymore. This could lead to a violation of the FIFO property if another product that must exit earlier is for instance still being processed.

- B. Only at most two products may be in the processing loop at any time. That is, at most at two of the *DISP*, *OP1*, *OP2* and *CHK* places there may be a product, at any time. This way, if a product keeps failing to be processed successfully, it can be redone over and over again, while the other product is at one of the operators. With three or more products in the processing loop, this is not possible. An exception to 'at most two products in the processing loop' rule is when a product has been checked and found to be successfully processed. Then, a third product may be present, as the successfully processed product can then leave the processing loop and at most two products will remain in the processing loop.

Then the supervisor restrictions are quite logical:

• The first restriction indicates when a product may *start* processing. Either one of its two conditions must hold for the *start* movement to be allowed. This directly follows from realization *B*. The first condition follows from the 'at most two products in the processing loop' rule. At most one product may be in the processing loop for another to enter it. The second condition describes the exception to this rule. There may be two products in the processing loop

if one of them is a successfully processed product about to leave the processing loop.

- The second and third restrictions indicate when a product may move to be checked. These two restrictions follow directly from realization *A*. A product *X* may only be moved to be checked, if there is no product that must exit earlier. Obviously, moving a product to the checker is physically only possible if there is a product at an operator, as otherwise there is no product to move. Also, it is only physically possible to move a product to the checker there is not already a product at the checker, as each place can only hold one product. This leaves only the dispatcher and other operator as places to be checked. If there would be an earlier product at the dispatcher or other operator, such a product would not be able to overtake the product about to be moved to the checker, leading to a violation of the FIFO property. Hence, both restrictions have to conditions, on for the dispatcher and one for the other operator. Either there must be no product at those places, or it is later product.

- The fourth restriction indicates when a product may *enter* the system. It only allows a product to enter if there are less than four products in the system. This means that the restriction ensures that at most four products are in the system at any time. Through realization *B* we know at most three products may be in the processing loop. Then only at most one of the *INOUT* and *DONE* places may contain a product, for a total of four products in the system. To understand why this is the case, consider the following:

- A product could be at the *INOUT* place. But then no product must be at the *DONE* place. If there were a product at the *DONE* place, there would be products at the *INOUT*, *DONE* and *CHK* places. The product at the *CHK* place could then not move to the *DONE* place, as that already has a product. Similarly, the product at the *DONE* place could then also not move to the already occupied *INOUT* place. And the product at the *INOUT* place could then not move to the *DISP* place, as the processing loop is already maximally filled. This would mean no product could move anywhere. This kind of deadlock is prevented by the fourth condition.

- A product could be at the *DONE* place. But then, by similar reasoning, no product must be at the *INOUT* place.

All of this is certainly a lot to consider! Would you have been able to figure all of this out by yourself? And how long would that have taken you? Considering this is only a simple example system with only one non-trivial requirement, it is clear that having some computer assistance when engineering a more realistic controller can be very useful.

#### 1.3.3. Example benefits of synthesis-based engineering

Finally, let us consider some of the benefits of synthesis-based engineering as it relates to this example:

- Synthesis automatically computes the optimal control conditions. It should now be clear that this can **save a lot of effort**.

- Manually engineering the controller can be quite tricky. It could easily lead to mistakes if certain scenarios are not properly accounted for. For instance, a restriction could be missed, or one of them could be incorrect. Synthesis can thus also **reduce human error**.

- Through synthesis you only have to specify the requirement and synthesis automatically generates a correct-by-construction controller, from which you can automatically generate the implementation. For the simple to specify but difficult to implement example requirement, this

allows you to **focus on** *what* **the controller should do** (the requirement), **rather than** *how* **the controller should do this** (the complex control conditions and their implementation).

- As an alternative to synthesis, we could apply formal verification on the system model to check whether the FIFO requirement holds. However, as the requirement does *not* hold on the system without a controller, we would get only a counter example representing a scenario indicating where the requirement does not hold. Likely, it would take several iterations and quite some thinking to manually arrive at the exact correct control conditions. **Compared to formal verification**, synthesis produces all the correct control conditions, **automatically and in a single iteration**.

- An engineer that develops the controller manually, may well impose severe restrictions to avoid much of the complexity of satisfying the FIFO requirement. The control conditions produced by synthesis however, are **minimally restrictive**. Products may enter the system, start processing, be processed in parallel, and leave the processing loop, whenever possible. This ensures the **maximum throughput** of the system can still be achieved.

- Synthesis-based engineering allows for a modular design. The various parts of the system, as well as the requirement, can be **modeled** separately. This makes it easy to adapt the system (model), to for instance allow products that do not require processing to bypass the processing loop. With minimal changes to the system model, and no changes to the requirement, a new supervisor can then be produced by the push of a button. This allows for **incremental development** of the system and its controller.

And again, consider that this is only a simple example system, with only a single requirement. Synthesis-based engineering has even more value when multiple, complex and related requirements need to be considered, or when controllers for many similar yet different systems need to be developed. See the section on benefits of synthesis-based engineering for further benefits of the approach.

Even though synthesis-based engineering has many benefits, companies should not underestimate how significantly different it is from traditional engineering. They should consider and manage the challenges particular to this engineering approach.

## 1.4. Synthesis-based engineering in practice

This section explains concretely how to use the CIF language and toolset to apply synthesis-based engineering of supervisory controllers. Before reading this section, please familiarize yourself with:

- The basics of the CIF language.

- The synthesis-based engineering approach.

#### **Development process**

The process to develop supervisory controllers using the synthesis-based engineering approach typically following several steps. We'll briefly discuss each of the steps and provide some practical guidance:

#### **Modeling the events**

Modeling the actions that can happen in the system as events.

#### Modeling the plant

Modeling the plant automata that represents the event behavior of the to-be-controlled system.

#### **Modeling plant relations**

Modeling the relations between the various plant automata.

#### Modeling the requirements

Modeling the requirements that restrict the behavior of the plant.

#### Marking

Dealing with marking of the plant and requirement automata.

#### **Supervisor synthesis**

Performing supervisor synthesis on the plant and requirements to automatically synthesize a supervisor.

#### Validation

Validating that the synthesized supervisor controls the system as desired.

#### **Controller implementation**

Implementing the validated supervisory controller using automatic code generation.

#### **Advanced topics**

Furthermore, the following more advanced information is available:

#### **Incremental controller development**

Explains how to incrementally develop your controller to prevent commonly encountered issues when applying synthesis-based engineering.

#### Resolving issues with too limited behavior

Explains how to resolve issues with too limited controlled system behavior, for instance due to conflicting requirements, revealed through synthesis or validation.

#### Supervisor synthesis performance

Explains how to resolve performance and memory issues for supervisor synthesis.